Les normes de mémoire vive sont en train de passer à l'ère de la DDR5, qui apporte un certain nombre d'améliorations et une augmentation considérable des performances par rapport à la DDR4. Cependant, la DDR et son parent plus rapide, la GDDR, ne sont pas vraiment aussi rapides que la norme HBM (mémoire à large bande passante) qui, selon Seok-Hee Lee, PDG de SK Hynix, pourrait être à la base de la fusion naturelle entre les CPU et la RAM.

Lors du symposium international sur la physique de la fiabilité de l'Institute of Electrical and Electronics Engineers, Seok-Hee Lee a présenté sa vision d'une norme de mémoire plus rapide qui nécessiterait une "convergence de la mémoire et de la logique." Lee présente une évolution plus graduelle en commençant par la HBM

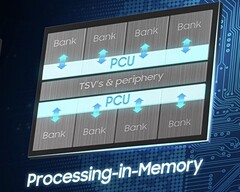

Comme la vitesse a été augmentée dans la mémoire à large bande passante en augmentant le nombre de canaux entre le CPU et la mémoire, la vitesse augmentera encore dans le Processing Near Memory (PNM), où le CPU et la mémoire existent dans un seul module. La vitesse augmentera encore dans le cas du traitement en mémoire (PIM), où l'unité centrale et la mémoire se trouvent dans un seul boîtier. Enfin, la vitesse augmentera encore dans la technologie CIM (Computing in Memory), où le CPU et la mémoire sont intégrés dans une seule puce, afin de fournir des systèmes informatiques de haute performance.

SK Hynix est actuellement le deuxième plus grand fabricant de mémoire au monde, mais il ne fabrique pas d'autres types de puces comme les CPU. Le PDG Lee appelle donc à une collaboration entre les géants des semi-conducteurs afin de former un écosystème capable de soutenir les nouveaux hybrides CPU+RAM : "Ce n'est qu'en établissant un partenariat stratégique pour l'innovation ouverte basé sur la collaboration et le partage avec les clients, les fournisseurs, le monde universitaire et le gouvernement, que nous pourrons façonner une nouvelle ère, qui poursuit une valeur à la fois économique et sociale."

Lee a également présenté une nouvelle norme appelée Compute Express Link (CXL) qui pourrait compléter le bus PCIe. La mémoire CXL est capable de déplacer les données rapidement et plus efficacement entre le CPU et les accélérateurs graphiques / de calcul ou les interfaces réseau intelligentes. "La mémoire CXL est préparée comme une solution qui non seulement élargit la bande passante et la capacité, mais réalise également la valeur d'une mémoire persistante, [...] une solution pour réduire l'écart entre les performances de la mémoire et les exigences de l'industrie."

Enfin, M. Lee a évoqué les efforts déployés pour améliorer les puces mémoire NAND intégrées dans les solutions de stockage SSD. Avec le passage à des nœuds de 10 nm et moins, SK Hynix pourrait éventuellement être en mesure de produire des puces NAND à 600 couches, ce qui devrait considérablement augmenter la capacité de stockage et les vitesses de transfert de données par rapport au plafond actuel de 176 couches.

Acheter le SAPPHIRE NITRO Radeon R9 Fury avec 4 Go HBM sur Newegg

Top 10

» Le Top 10 des PC portables multimédia

» Le Top 10 des PC portables de jeu

» Le Top 10 des PC portables de jeu légers

» Le Top 10 des ordinateurs portables bureautiques

» Le Top 10 des PC portables bureautiques premium/professionnels

» Le Top 10 des Stations de travail mobiles

» Le Top 10 des Ultraportables

» Le Top 10 des Ultrabooks

» Le Top 10 des Convertibles

» Le Top 10 des Tablettes

» Le Top 10 des Tablettes Windows

» Le Top 10 des Smartphones

» Le Top 10 des PC Portables á moins de 300 euros

» Le Top 10 des PC Portables á moins de 500 euros

» Le Top 25 des meilleurs écrans d'ordinateurs